| |

|

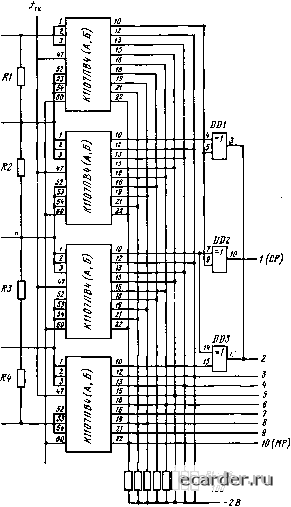

Слаботочка Книги 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 [56] 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 Аа Уш {к точке А) jj 5» I - (кточиеВ) (кточкеС) Перепопиеиие / (CF) . 2 3 4 5 6 7 •8 3(ПР) TTTTT - Схема подключения входов и выходов двух БИС К1107ПВ4 (А, Б) при увеличении числа разрядов АЦП до девяти. Точки подключения Л, В, С указаны на типовой схеме включения Схема позволяет увеличить число разрядов блока АЦП до десяти. Соответствующие друг другу Щ!фровые выходы БИС АЦП (выводы 12, 13, 15, 16, 18, 19, 21, 22) соединяются попарно и нагружаются общими резисторами, на которых фактически выполняется функция ИЛИ. В диапазоне входного сигнала -2,5...0 В работает БИС D1, а в диапазоне 0...2,5 В-БИС D2. Точностные характеристики блока из двух БИС АЦП обеспечиваются необходимыми регулировками, справедливыми для включения одной БИС АЦП. Для уменьшения динамической составляющей погрешности БИС АЦП токонесущие дорожки к ней рекомендуется проводить одинаковой длины, причем цифровые выходы необходимо соединять дорожками, вьшолнеиными в виде согласованных микрополосковых линий. (к точке А) 0.75 и„„ 0.5U, O.ZSU (н точке С) (к точке В) Переполнение ВВ1-ВВЗ КС500ЛП1В7П (K500BnfB7H)  Схема включения входов и выходов четырех БИС К1107ПВ4 (А, Б) при увеличении числа разрядов АЦП до десяти. Точки подключения А, fi, С указаны на типовой схеме включения Данная схема включения позволяет увеличить число разрядов блока АЦП до 10. Соответствующие друг другу цифровые выходы БИС АЦП по аналогии с предыдущей схемой включения соединяются между собой. Диапазон опорных напряжений должен быть поделен поровну между соответствующими входами каждой из БИС АЦП. При этом следует исходить из того, что опорные напряжения не должны превышать установленные предельные значения. Каждая микросхема работает в диапазоне (l/„„i -{/„„2)/4= 1,25 В, в котором обеспечивается нелинейность ±0,5 MP. Для получения эквивалентного десятиразрядного кода применяются три цифровые схемы Исключающее ИЛИ (например, серии КС500). Здесь необходимо обеспечить одновременное поступление входных и тактовых сигналов на каждую БИС АЦП, согласовать цифровые выходы с нагрузкой с помощью микрополосковых линий. Входная емкость четырех параллельно включенных БИС по аналЬговому входу увеличивается в 4 раза (по сравнению с одной). Дополнительная литература Быстродействующие интегральные микросхемы ЦАП и АЦП и измерение их параметров А.-Й. К. Марцинкявичюс, Э.-А. К. Багданскис, Р. Л. Пошюнас и др./Под общ. ред. А.-Й. К. Марцинкявичюса и Э.-А. К. Багданскиса/М.: Радио и связь, 1988.-С. 80--100. КР1107ПВ5А, КР1107ПВ5Б Микросхемы представляют собой БИС быстродействующих шестиразрядных АЦП считывания с нормированной полосой частот входного сигнала. Предназначены для преобразования его амплитуды в диапазоне ±2 В в параллельный двоичный цифровой код. Сопрягаются по выходу с цифровыми ЭСЛ-мнкросхе-мами. Выполнены по биполярной планарно-эпитаксиальной технологии п-р-п транзисторов с изоляцией обратносмещенными р-п переходами и двухуровневой металлизацией. Резисторный делитель опорного напряжения выполнен в диффузионном слое глубокого коллектора. Содержат около 1500 интегральных элементов. Конструктивно оформлены в пластмассовом 24-выводном корпусе типа 239.24-2. Масса микросхем не превышает 1,5 г. Микросхемы КР1107ПВ5А, КР1107ПВ5Б используются в быстродействующих системах сбора и обработки информации, вычислительной и измерительной аппаратуре, устройствах телеметрии и цифрового телевидения, диагностических и медицинских приборах, в устройствах автоматики и связи. 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 [56] 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 |

||||||||||||||||||||||||||||||||