| |

|

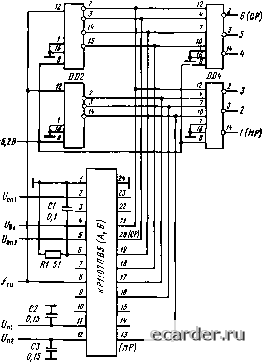

Слаботочка Книги 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 [59] 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 - 181 - КР1107ПВ5(А, Б) Схемы включения Типовая схема включения БИС АЦП КР1107ПВ5 (А, Б)  {К500ЛГ1101) Схема позволяет устранить нежелательные эффекты неопределенности выходного кода и самовозбуждения АЦП из-за возникновения паразитной положительной обратной связи в цепях компарнрования и дешифрации за счет блокирования результатов преобразования в режиме выборки. Сигнал логической 1 с выходов элементов ИЛИ DDI и DD2 запирает транзисторные повторители в выходном каскаде АЦП, тем самым разрывая цепь обратной связи. Цифровые микросхемы DDi, DD4 используются для стабилизации выходного кода в моменты перегрузки АЦП по входу, что особенно важно при включении двух и более БИС. Возможно включение БИС АЦП КР1107ПВ5А, КР1107ПВ5Б с формирователем регулируемых опорных напряжений (точки подключения А и Q, входным буферным усилителем (точка подключения В), формирователем напряжения гистерезиса (точка подключения D). Установка опорных напряжений в диапазоне ±2 В производится резисторами R24 и R27. Возможно применение стабилитрона VD8 типа КС133А. и„п1 (к точке А) DI {к точке в) /та и„„г(кточкеС) Переаояие-Hue -2 -J « - i ?m ШК1-ВВ m -2 в f/„„, (к точке A) Отг /т. dx [к точке C) (к точке В) Переполнение -1(СР) -5 -S RI-RS 100 -2 В Схема включения входов и выходов двух БИС КР1107ПВ5 (А, Б) при увеличении числа разрядов АЦП до семи. Точки подключения А, В, С указаны на типовой схеме включения Схема включения входов и выходов четырех БИС КР1107ПВ5 (А, Б) при увеличении числа разрядов АЦП до восьми. Точки подключения А, В, С указаны на типовой схеме включения - 183 - КР1107ПВ5 (А, Б) Схема позволяет увеличить число разрядов блока АЦП до семи. Соответствующие друг другу цифровые выходы БИС АЦП (выводы 13,16, 17-20) соединяются попарно и нагружаются общими резисторами сопротивлением 100 Ом + 5%. В диапазоне -2...0 В работает БИС D1, а в диапазоне 0...2 В -БИС 1)2. Точностные характеристики блока из двух БИС АЦП обеспечиваются необходимыми регулировками (/„п! и оп2- Для уменьшения динамической составляющей погрешности рекомендуется для каждой БИС АЦП провести токонесущие дорожки одинаковой длины. Цифровые выходы необходимо соединять дорожками, выполненными в виде согласованных микрополосковых линий. Данная схема позволяет увеличить число разрядов блока АЦП до восьми. Соответствующие друг другу цифровые выходы БИС АЦП соединяются между собой (по аналогии с приведенной выше схемой включения). Диапазон опорных напряжений делится поровну между соответствующими входами БИС АЦП. Значения опорных напряжений не должны при этом превышать предельно допустимые 12,51 В. Для сохранения высокой линейности преобразования желательно, чтобы диапазон входных напряжений для каждой БИС АЦП удовлетворял соотношению (С/„„, -С/„„2)/4= 1,25 В. Для получения восьмиразрядного цифрового кода на выходах блока АЦП используются схемы Исключающее ИЛИ (серии К500, KCSOO). Здесь необходимо обеспечить одновременное поступление входных сигналов и тактовых импульсов на БИС АЦП. Для обеспечения наибольшего быстродействия преобразования рекомендуется согласование выходов БИС АЦП с нагрузкой с помощью микрополосковых линий. За счет увеличения входной эквивалентной емкости диапазон частот входного сигнала блока АЦП может сузиться наполовину, т.е. до 10...12 МГц. Дополнительная литература Федорков Б. Г., Телец В. А. Микросхемы ЦАП и АЦП: функционирование, параметры, применение.- М.: Энергоатомиздат, 1990.- С. 185-187. 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 [59] 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 |